T/CASAS 042-2024 碳化硅金属氧化物半导体场效应晶体管(SiC MOSFET)高温栅偏试验方法 ,该文件为pdf格式 ,请用户放心下载!

尊敬的用户你们好,你们的支持是我们前进的动力,网站收集的文件并免费分享都是不容易,如果你觉得本站不错的话,可以收藏并分享给你周围的朋友。

如果你觉得网站不错,找不到本网站,可以百度、360搜搜,搜狗, 神马搜索关键词“文档天下”,就可以找到本网站。也可以保存到浏览器书签里。

收费文件即表明收集不易,也是你们支持,信任本网站的理由!真心非常感谢大家一直以来的理解和支持!

《T/CASAS 042-2024 碳化硅金属氧化物半导体场效应晶体管(SiC MOSFET)高温栅偏试验方法》的主要内容详细总结。

1. 文档范围和应用

- 适用范围:本文件适用于SiC MOSFET功率器件(分立器件)和功率模块的可靠性评估,旨在通过高温栅偏试验模拟加速老化条件,暴露器件在高温和高电压应力下的潜在缺陷。

- 核心目的:试验用于评估栅极电介质的完整性(如经时介电层击穿)、半导体与电介质边界层的退化(表现为阈值电压和米勒电容变化),以及可动离子污染导致的性能退化。这有助于在短时间内预测器件在正常工况下的寿命和可靠性,特别适用于航天、航空、石油勘探、核能等高需求领域。

- 相关标准:文档引用GB/T 1.1-2020、GB/T 4586-1994、T/CASAS 002-2021和T/CASAS 006-2020等标准,确保试验方法的规范性和兼容性。

2. 关键术语和定义

文档第3章定义了SiC MOSFET试验中的核心术语,确保测试一致性:

- 电学参数:

- 栅-源电压(

V_{GS}):栅极与源极之间的电压。 - 漏-源电压(

V_{DS}):漏极与源极之间的电压。 - 栅极漏电流(

I_{GSS}):栅极在最大电压下的漏泄电流,分为正偏压(I_{GSS+})和负偏压(I_{GSS-})。 - 漏极漏电流(

I_{DSS}):漏极在规定高压下的漏泄电流。 - 阈值电压(

V_{GS(th)}):漏极电流达到规定低值时的栅-源电压。 - 漏-源导通电阻(

R_{DS(on)}):在指定栅压、电流和结温下的导通电阻。 - 体二极管正向压降(

V_F / V_{SD}):漏源反向电压下的正向压降。 - 击穿电压(

V_{BR}):漏极电流达到规定值时的漏-源电压。

- 栅-源电压(

- 温度参数:

- 环境温度(

T_a)、管壳温度(T_c)、散热器温度(T_s)、结温(T_j)和虚拟结温(T_{vj})。其中,T_{vj}是通过电学方法间接测量的结温,用于替代无法直接测量的T_j。

- 环境温度(

- 其他关键概念:如经时介电层击穿(TDDB)、界面陷阱等,强调SiC/SiO2界面的缺陷是主要失效根源。

3. 试验装置要求

文档第4章详细规定了试验装置的功能和性能指标,确保测试环境稳定可靠:

- 试验环境要求:

- 温度范围:需覆盖25°C至300°C,温度波动度优于1°C,容许偏差优于±2°C,升温速率优于1°C/min。

- 环境控制:使用恒温槽、热平台或温箱提供均匀高温环境,并配备实时温度监测系统(如传感器),确保芯片结温(

T_{vj})达到指定最大值(如器件规格书中的最高值),同时外壳温度在允许范围内(±10K)。

- 试验装置组成:

- 功率偏置单元(电源):需具备恒压/恒流输出模式,电压和电流范围覆盖器件额定值(例如,30V量程分辨率≤1mV,精度±(0.03%量程+10)mV)。电源输出纹波和噪声需低,并内置过压、过流、过温保护功能。

- 温度控制系统:确保快速升降温能力,并具备安全保护机制。

- 测量设备:包括高精度示波器、电流表、电压表和源测量单元,要求微弱信号测量能力强(例如,100nA量程分辨率优于10pA,精度±(0.1%量程+0.5)nA)。推荐采用标准化试验系统,以减少寄生参数影响(如使用四线制开尔文连接),并在测试前进行全面校准。

- 整体要求:装置需支持数据实时采集和存储,防止长时间测试数据丢失,并针对SiC MOSFET特性优化(如处理阈值电压迟滞效应)。

4. 试验方法步骤

文档第5章(5.1目的和5.2测试)是核心,描述了试验流程和具体操作。试验分为正栅压偏置( V_{GS} = V_{GS,\text{max}} )和负栅压偏置( V_{GS} = V_{GS,\text{min}} )两种模式,试验时间至少1000小时,环境温度设置为器件最大虚拟结温( T_{vj,\text{max}} ),漏源电压( V_{DS} )设为0V(即漏极短接至源极)。样品数量要求:分立器件建议154个(正/负偏置各77个),功率模块建议6个(正/负偏置各3个)。

测试流程详细步骤:

- a) 样品准备:去除样品表面污染物,焊接或安装到测试夹具上(确保良好热连接和电气连接),采用四线制开尔文连接法减少接线电阻影响。样品需经目检和初始电参数测试(包括

I_{GSS+}、I_{GSS-}、I_{DSS}、R_{DS(on)}、V_{GS(th)}、V_F、V_{BR}),确保无缺陷。 - b) 最初测试:记录所有电学参数初始值,作为后续失效判定的基准。需注意阈值电压(

V_{GS(th)})测量时的迟滞效应,测试前需进行统一预处理。 - c) 温度及偏置设置:设置温度控制系统至指定

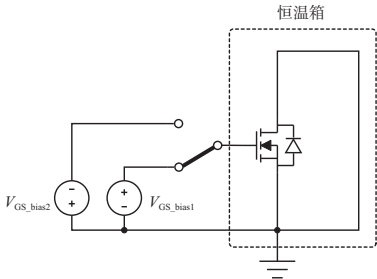

T_{vj},并配置偏置电源输出(正压或负压)。升温前10分钟内施加偏置电压。 - d) HTGB试验执行:参考图1电路,将偏置电源(

V_{GS\_bias1}或V_{GS\_bias2})连接到栅极和源极,漏极短接至源极。试验过程中,V_{DS} = 0V。

- e) 中间测试:试验期间实时监测并记录栅极漏电流(

I_{GSS}),检测异常变化。 - f) 冷却处理:试验结束后,在去除偏置前将器件冷却至55°C以下。冷却过程中,偏置中断不超过1分钟可忽略;否则需按文档规定处理(见表2)。

- g) 最终测试:冷却后96小时内完成最终电参数测试(同最初测试项目)。若超时,需按表2附加应力时间(例如,超时168小时需额外48小时应力)。测试需注意迟滞效应的统一处理。

- h) 数据记录:全程记录应力条件(温度、电压、时间)、监测数据(如

I_{GSS})和任何异常现象。

关键注意事项:

- 试验聚焦芯片级失效,需确保散热器温度(

T_s)或外壳温度(T_c)达到T_{vj},并在报告中注明。 - 样品安装时避免局部过热,测试系统需定期维护校准。

- 表2规定了超时处理规则:超出96小时未测试时,每168小时增加24小时附加应力时间。

5. 失效判定标准

文档第6章定义了试验后的失效判定依据,基于电学参数变化或外观损坏。任何样品满足以下任一条即判为失效;但非样品因素(如操作失误或装置故障)导致的失效不计入批次失效,需记录分析并经用户同意后重试。

- 电学参数失效判据(表3):

R_{DS(on)}:变化率≥20%,或超出规格书最大/最小值。V_F:变化率≥5%,或超出规格书最大/最小值。V_{BR}:变化率≥20%,或低于规格书最小值。V_{GS(th)}:变化率≥20%,或超出规格书最大/最小值。I_{DSS}:变化率≥1000%,或高于规格书最大值。I_{GSS}(正偏或负偏):变化率≥1000%,或高于规格书最大值。

- 外观失效:样品出现任何物理损坏(如裂纹或烧毁)。

- 补充失效判定:可根据用户需求增加其他判定标准,但需在报告中说明。

6. 测试报告要求

文档第7章规定了测试报告的必要内容,确保数据可追溯和可复现:

- 报告要素:包括样品名称和数量、试验条件(偏置电压、温度、时间)、连续监测数据(如

I_{GSS})、试验前后的电参数对比(I_{DSS}、I_{GSS+}、I_{GSS-}、R_{DS(on)}、V_{GS(th)}、V_F、V_{BR}),以及任何补充项目(如冷却记录或异常现象)。 - 记录表示例:附录A提供了标准化的试验记录表模板(见表A.1),涵盖产品信息、测试仪器、环境条件、技术要求和参数记录,便于统一数据管理。

- 整体要求:报告需详细记录校准信息(仪器型号、编号和有效期),并引用规范性标准。

7. 附录和参考文献

- 附录A(资料性):提供SiC MOSFET高温栅偏试验记录表的示例(表A.1),包括样品编号、试验前后参数对比和失效勾选项,用于实际测试中的结构化记录。

- 参考文献:文档引用了IEC、AEC-Q101、AQG 324、JESD等国际和行业标准(如IEC 60747-8:2021、JEP 183A),强调本试验方法与全球可靠性测试规范的兼容性。

整体总结

本文件系统性地定义了SiC MOSFET高温栅偏试验的全流程,从装置准备到失效判定,突出了其在模拟极端工况下的加速老化作用。核心创新点包括针对SiC材料特性(如界面陷阱)的测试优化、严格的温度/电压控制要求,以及详细的失效机制覆盖(如TDDB和离子污染)。试验方法强调可重复性和安全性,适用于器件研发、质量验证和生产监控,能有效提升SiC MOSFET在高温高湿应用中的可靠性。用户实施时需严格遵守文档中的参数阈值和报告规范,以确保测试结果的有效性和可比性。

评论